Singxer SU-6 USB Digital Interface XMOS XU208 CPLD Femtosecond

---SpecificationsSplit---

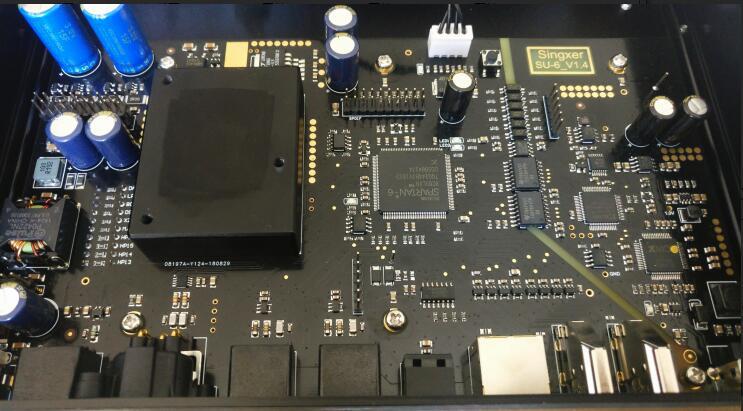

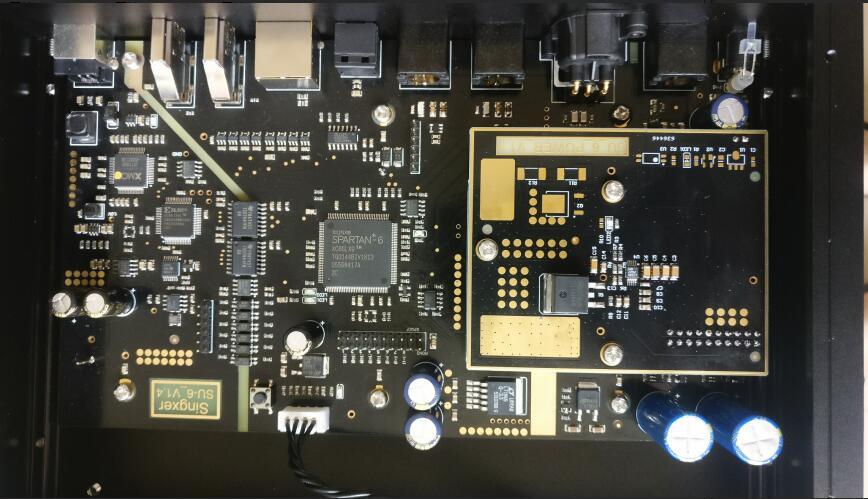

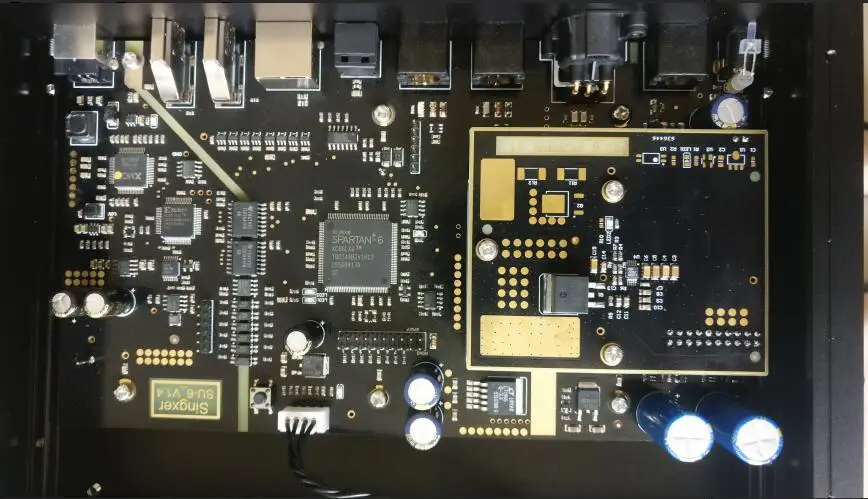

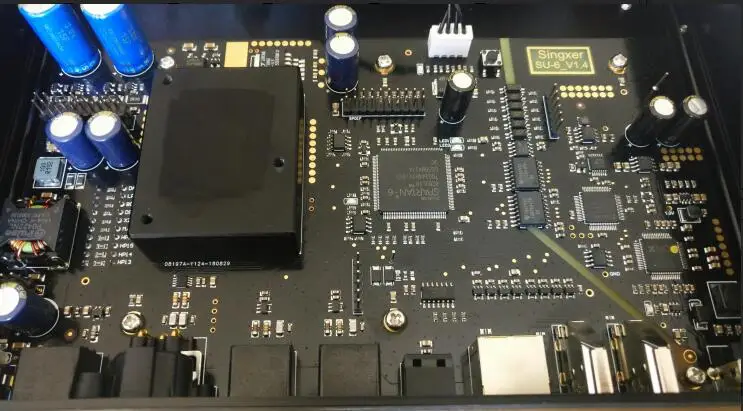

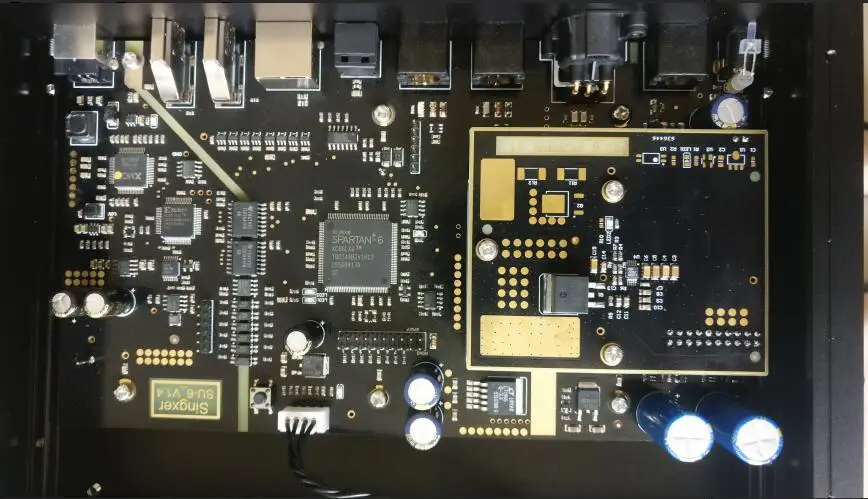

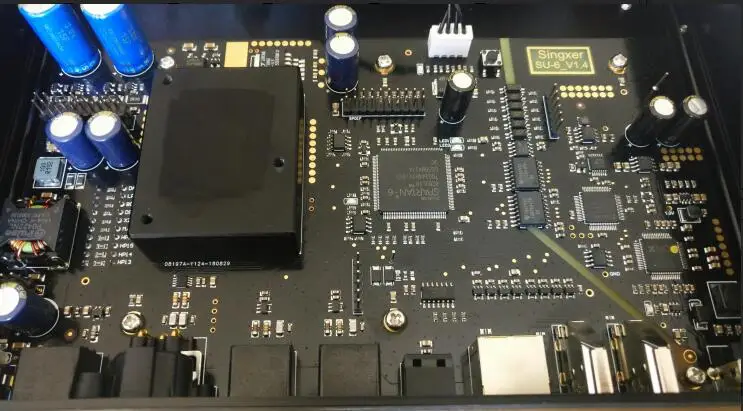

The SU-6 digital interface is a new generation of high-performance USB digital audio interface. It uses XMOS' latest xCORE-200 series and Xilinx's high-performance large-scale PGA chip. The SU-6 is a digital interface using a thermostat-level clock system. Crystek's two CCHD-957 femtosecond crystal oscillators provide a solid foundation for the superior audio signal quality of the SU-6 output. The SU-6 digital interface uses a standard USB2.0 input interface, while the SU-6 has a rich output interface, including S/PDI for fiber/coaxial RCA and BNC outputs, AES/EBU for XLR balanced output, RJ45 and HDMI interfaces. Output I2S (including DSD ON signal), clock output supports MCLK main clock and WCLK word clock. The power system design was optimized and the audio section was powered by a 7.5F (7.5 million uf) supercapacitor.

SU-6 is newly developed USB interface, which is positioned at the high-end interface. Compared with previous products, we mainly use the following four new self-developed technologies:

1, built-in CPLD pre-shaping technology, FPGA-based source synchronization technology re-shaping the isolated I2S signal, thus eliminating the additive jitter caused by the isolation chip.

2, the newly designed FPGA algorithm, built-in FIFO buffers the data and then outputs, SPDIF output is re-encoded by FPGA, so that the coaxial output can support PCM 384K and DSD DOP128 at the highest.

3, using CRYSTEK's CCHD-957 high-performance femtosecond crystal oscillator, with the self-developed constant temperature system and ultra-low noise super capacitor power supply system, further improve the short-stability performance of the clock.

4. Original single clock system, all circuits of the whole machine adopt synchronous clock design, in which USB clock is synthesized by PLL derived from femtosecond clock.

PCM: 44.1KHz, 48KHz, 88.2KHz, 96KHz,

176.4KHz, 192KHz, 352.8KHz, 384KHz

[I2S out and WCLK out support all sampling rates, S/PDI and AES/EBU support up to 384K, of which fiber supports up to 192K]

DSD: 2.8 MHz (DSD64) - DoP, native

5.6 MHz (DSD128) - DoP, native

11.2 MHz (DSD256) - DoP, native

22.5 MHz (DSD512) - Native

[I2S out supports all DSD formats, S/PDI and AES/EBU support DSD128 DOP mode, where fiber supports up to DOP64]

Bit width: up to 32 bit over I2S output

Highly 24 bit over S/PDI, AES/EBU

Electrical standards for each interface:

System compatibility:

Flexible I2S and clock configuration:

When the switch 5 is at the time of O, the clock outputs MCLK, and when it is ON, the clock outputs WCK;

The switch 6 is configured with the frequency of MCLK, when O is 22.5792M/24.576M, and when ON is 45.1584M/49.152M;

The configuration of switch 6 is valid for CLK OUT, RJ45-I2S, and HDMI-I2S.

Note: Coaxial, fiber, AES/EBU output is not affected by the above DIP switch; The line sequence of RJ45-I2S is fixed, and it needs to adapt to different interfaces. Users need to customize the network cable.

---SpecificationsSplit---

The SU-6 digital interface is a new generation of high-performance USB digital audio interface. It uses XMOS' latest xCORE-200 series and Xilinx's high-performance large-scale PGA chip. The SU-6 is a digital interface using a thermostat-level clock system. Crystek's two CCHD-957 femtosecond crystal oscillators provide a solid foundation for the superior audio signal quality of the SU-6 output. The SU-6 digital interface uses a standard USB2.0 input interface, while the SU-6 has a rich output interface, including S/PDI for fiber/coaxial RCA and BNC outputs, AES/EBU for XLR balanced output, RJ45 and HDMI interfaces. Output I2S (including DSD ON signal), clock output supports MCLK main clock and WCLK word clock. The power system design was optimized and the audio section was powered by a 7.5F (7.5 million uf) supercapacitor.

SU-6 is newly developed USB interface, which is positioned at the high-end interface. Compared with previous products, we mainly use the following four new self-developed technologies:

1, built-in CPLD pre-shaping technology, FPGA-based source synchronization technology re-shaping the isolated I2S signal, thus eliminating the additive jitter caused by the isolation chip.

2, the newly designed FPGA algorithm, built-in FIFO buffers the data and then outputs, SPDIF output is re-encoded by FPGA, so that the coaxial output can support PCM 384K and DSD DOP128 at the highest.

3, using CRYSTEK's CCHD-957 high-performance femtosecond crystal oscillator, with the self-developed constant temperature system and ultra-low noise super capacitor power supply system, further improve the short-stability performance of the clock.

4. Original single clock system, all circuits of the whole machine adopt synchronous clock design, in which USB clock is synthesized by PLL derived from femtosecond clock.

Questions & Answers

Have a Question?

Be the first to ask a question about this.

Questions & Answers

Have a Question?

Be the first to ask a question about this.